Sidste uge hos Apple det blev registreret til ham et patent på en teknologi kaldet Makroskalar som har den rolle at forbedre ydeevnen af en processor til mobile terminaler væsentligt. Dette er virksomhedens fjerde patent relateret til denne teknologi, og det ser ud til, at Apple forbereder det til implementering i nogle af dets produkter. Den interessante del af denne teknologi ligger i det faktum, at Apple har patenteret det i flere lande rundt om i verden, så det kan lancere i den nærmeste fremtid et produkt, der kunne få det implementeret.

I begyndelsen af sidste uge offentliggjorde US Patent & Trademark Office en overraskende varemærkeansøgning fra Apple for ordet "Macroscalar." En anden varemærkeansøgning for dette dukkede også op i Hong Kongs IP Offices database i weekenden. Selvfølgelig betyder en varemærkeansøgning i sig selv absolut ingenting. Men det er ikke tilfældet her. Apples "Macroscalar" er det ikke lige en ny markedsføringslinje; det er en processorarkitektur, der har været undervejs hos Apple siden 2004. Faktisk ejer Apple mindst fire tildelte patenter på teknologien, som endnu ikke er kommet frem i lyset.

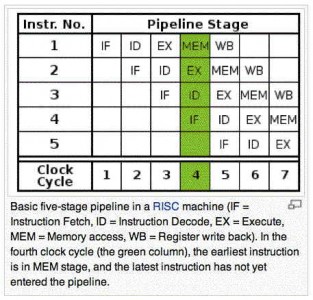

Apple har arbejdet på denne teknologi siden 2004 og i bund og grund forbedrer den en processors computerkraft betydeligt ved at fjerne fokus fra frekvensen og sætte den på instruktion pipelining hvilket ville give processorer mulighed for at udføre flere kommandoer på samme tid med færre forhindringer at overvinde. Hastighed er ikke det eneste kendetegn ved de nye processorer, fordi de vil bruge endnu mindre energi for at fungere, så vi taler om et rigtigt "es i ærmet" for Apple, som ikke skulle bruge quad-core processorer i iDevices for at få hævet ydeevne.

Efterhånden som clockfrekvenserne fortsætter med at stige som svar på øgede krav til ydeevne, er strøm også steget, mens dybere rørledninger har udvist en aftagende effekt på antallet af instruktioner pr. cyklus (IPC) opnået i virkelige situationer, hvilket yderligere bidrager til strømmen dissipationsproblem gennem ineffektivitet. En række forskellige mekanismer er opstået gennem årene, der forsøger at redde instruktionsniveau parallelisme (ILP), såsom SMT (samtidig multi-threading) og VLIW (meget langt instruktionsord) og udelukket udførelse, nogle med mere succes end andre. Den klassiske kompileringstidsoptimering, der tillader mere effektiv udnyttelse af længere pipelines, er sløjfeudrulning. Desværre mangler de fleste processorer det nødvendige antal programregistre til at tillade nok udrulning til fuldt ud at mætte dybere rørledninger. At øge antallet af registre uden at kompromittere softwarekompatibiliteten er også problematisk. Ydermere kan mange typer sløjfer simpelthen ikke udrulles, såsom dem, der implementerer dataafhængig kontrol-flow, som er den samme klasse af sløjfer, der er hårdest ramt af dybere rørledninger.

Selvom teknologien i sig selv ser fantastisk ud, er problemet, at Apple muligvis ikke har den klar til medtagelse i A6-chippen, der ville være inkluderet i iPad 3 og iPhone 5.

Da Apple leverer sine egne compilere såvel som at designe CPU'er, er det unikt positioneret til at tilbyde en komplet makroskalær løsning til sin store gruppe af iOS-udviklere, hvilket yderligere udvider pris/ydelseskløften mellem den og iPad-wannabes. Er det et gennembrud? Det kunne være, hvis de effektiviseringer, det lover, kan realiseres i praksis. Vi bliver nødt til at se, hvor gode Apples compileringeniører er.