La semaine dernière chez Apple cela lui a été enregistré un brevet pour une technologie appelée Macroscalaire qui a pour rôle d’améliorer significativement les performances d’un processeur pour terminaux mobiles. Il s'agit du quatrième brevet de l'entreprise lié à cette technologie et il semble qu'Apple prépare sa mise en œuvre dans certains de ses produits. La partie intéressante de cette technologie réside dans le fait qu'Apple l'a brevetée dans plusieurs pays du monde, elle pourrait donc lancer dans un avenir proche un produit qui pourrait la mettre en œuvre.

Au début de la semaine dernière, l'Office américain des brevets et des marques a publié une surprenante demande de marque déposée par Apple pour le mot « Macroscalar ». Un deuxième dépôt de marque à ce sujet est également apparu dans la base de données de l'IP Office de Hong Kong au cours du week-end. Bien entendu, un dépôt de marque en soi ne veut absolument rien dire. Mais ce n'est pas le cas ici. Le "Macroscalar" d'Apple ne l'est pas juste une nouvelle ligne marketing ; il s'agit d'une architecture de processeur en préparation chez Apple depuis 2004. En fait, Apple possède au moins quatre brevets accordés sur la technologie qui n'a pas encore été révélée.

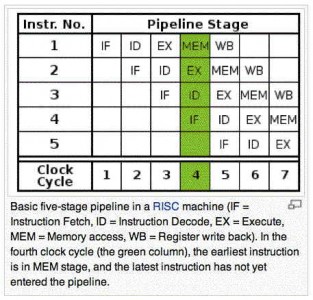

Apple travaille sur cette technologie depuis 2004 et, essentiellement, elle améliore considérablement la puissance de calcul d'un processeur en détournant l'attention de la fréquence et en la mettant sur pipeline d'instructions ce qui permettrait aux processeurs d'exécuter plus de commandes en même temps avec moins d'obstacles à surmonter. La vitesse n'est pas la seule caractéristique des nouveaux processeurs car ils consommeront encore moins d'énergie pour fonctionner, nous parlons donc d'un véritable "as dans la manche" pour Apple, qui n'aurait pas à utiliser de processeurs quad-core dans les iDevices pour obtenir des performances élevées.

À mesure que les fréquences d'horloge continuent d'augmenter en réponse aux demandes croissantes de performances, la puissance a également augmenté, tandis que les pipelines plus profonds ont montré un effet décroissant sur le nombre d'instructions par cycle (IPC) obtenues dans des situations réelles, ce qui contribue encore à la puissance. problème de dissipation par inefficacité. Une variété de mécanismes sont apparus au fil des années pour tenter de sauver le parallélisme au niveau des instructions (ILP), tels que SMT (multi-threading simultané) et VLIW (mot d'instruction très long) et l'exécution dans le désordre, certains avec plus de succès. que d'autres. L'optimisation classique au moment de la compilation qui permet une utilisation plus efficace de pipelines plus longs est le déroulement de boucles. Malheureusement, la plupart des processeurs ne disposent pas du nombre requis de registres de programme pour permettre un déroulement suffisant pour saturer complètement les pipelines plus profonds. Augmenter le nombre de registres sans compromettre la compatibilité logicielle est également problématique. En outre, de nombreux types de boucles ne peuvent tout simplement pas être déroulés, comme celles qui implémentent un flux de contrôle dépendant des données, qui est la même classe de boucles qui est la plus durement touchée par les pipelines plus profonds.

Bien que la technologie elle-même semble excellente, le problème est qu'Apple n'est peut-être pas prête à l'inclure dans la puce A6 qui serait incluse dans l'iPad 3 et l'iPhone 5.

Étant donné qu'Apple fournit ses propres compilateurs et conçoit des processeurs, elle est dans une position unique pour offrir une solution macroscalaire complète à son large groupe de développeurs iOS, élargissant encore l'écart prix/performances entre elle et les aspirants iPad. Est-ce une avancée ? Cela pourrait l’être si les gains d’efficacité promis pouvaient être réalisés dans la pratique. Nous devrons voir à quel point les ingénieurs compilateurs d'Apple sont bons.