La settimana scorsa ad Apple era intestato a lui un brevetto per una tecnologia chiamata Macroscalare che ha il ruolo di migliorare sensibilmente le prestazioni di un processore per terminali mobili. Questo è il quarto brevetto dell'azienda relativo a questa tecnologia e sembra che Apple lo stia preparando per l'implementazione in alcuni dei suoi prodotti. La parte interessante di questa tecnologia sta nel fatto che Apple l'ha brevettata in diversi paesi del mondo, quindi potrebbe lanciare nel prossimo futuro un prodotto che la possa implementare.

All'inizio della scorsa settimana l'Ufficio Brevetti e Marchi degli Stati Uniti ha pubblicato una sorprendente domanda di marchio da parte di Apple per la parola "Macroscalar". Un secondo deposito di marchio per questo è apparso anche nel database dell'IP Office di Hong Kong durante il fine settimana. Naturalmente il deposito di un marchio di per sé non significa assolutamente nulla. Ma non è questo il caso qui. Il "Macroscalar" di Apple non lo è ad appena una nuova linea di marketing; si tratta di un'architettura di processore in lavorazione presso Apple dal 2004. In effetti, Apple possiede almeno quattro brevetti concessi sulla tecnologia che deve ancora venire alla luce.

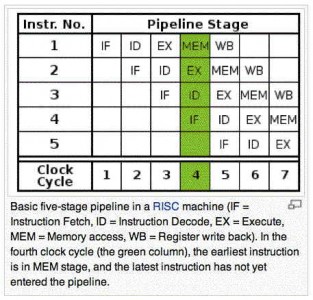

Apple lavora su questa tecnologia dal 2004 e in sostanza migliora notevolmente la potenza di calcolo di un processore distogliendo l'attenzione dalla frequenza e mettendola su pipeline di istruzioni che consentirebbe ai processori di eseguire più comandi contemporaneamente con meno ostacoli da superare. La velocità non è l'unica caratteristica dei nuovi processori perché consumeranno ancora meno energia per funzionare, parliamo quindi di un vero e proprio "asso nella manica" per Apple, che non dovrebbe utilizzare processori quad-core negli iDevices per ottenere prestazioni aumentate.

Poiché le frequenze di clock continuano ad aumentare in risposta alle crescenti richieste di prestazioni, anche la potenza è aumentata, mentre le pipeline più profonde hanno mostrato un effetto decrescente sul numero di istruzioni per ciclo (IPC) ottenuto nelle situazioni del mondo reale, il che contribuisce ulteriormente alla potenza. problema della dissipazione per inefficienza. Nel corso degli anni sono emersi numerosi meccanismi che tentano di salvare il parallelismo a livello di istruzione (ILP), come SMT (multi-threading simultaneo) e VLIW (parola di istruzioni molto lunga) e l'esecuzione fuori ordine, alcuni con maggiore successo di altri. La classica ottimizzazione in fase di compilazione che consente un utilizzo più efficace di pipeline più lunghe è lo srotolamento del ciclo. Sfortunatamente, la maggior parte dei processori non dispone del numero necessario di registri di programma per consentire uno srotolamento sufficiente a saturare completamente le pipeline più profonde. Anche aumentare il numero di registri senza compromettere la compatibilità del software è problematico. Inoltre, molti tipi di loop semplicemente non possono essere srotolati, come quelli che implementano il flusso di controllo dipendente dai dati, che è la stessa classe di loop colpita più duramente dalle pipeline più profonde.

Anche se la tecnologia in sé sembra ottima, il problema è che Apple potrebbe non averla pronta per essere inclusa nel chip A6 che verrebbe incluso nell'iPad 3 e nell'iPhone 5.

Poiché Apple fornisce i propri compilatori e progetta CPU, è in una posizione unica per offrire una soluzione macroscalare completa alla sua vasta fascia di sviluppatori iOS, ampliando ulteriormente il divario prezzo/prestazioni tra lei e gli aspiranti iPad. È una svolta? Potrebbe esserlo se l’efficienza promessa potesse essere realizzata nella pratica. Dovremo vedere quanto sono bravi gli ingegneri compilatori di Apple.