Ostatni tydzień w Apple było na niego zarejestrowane patent na technologię tzw makroskalarny który ma za zadanie znacznie poprawić wydajność procesora dla terminali mobilnych. To już czwarty patent firmy związany z tą technologią i wygląda na to, że Apple przygotowuje go do wdrożenia w części swoich produktów. Interesująca część tej technologii polega na tym, że Apple opatentował ją w kilku krajach na całym świecie, dzięki czemu może w niedalekiej przyszłości wypuścić na rynek produkt, który mógłby ją wdrożyć.

Na początku zeszłego tygodnia Amerykański Urząd Patentów i Znaków Towarowych opublikował zaskakujący wniosek Apple dotyczący znaku towarowego dla słowa „Macroscalar”. W weekend w bazie danych Urzędu ds. własności intelektualnej w Hongkongu pojawiło się również drugie zgłoszenie znaku towarowego w tej sprawie. Oczywiście samo zgłoszenie znaku towarowego nic nie znaczy. Ale tak nie jest w tym przypadku. „Macroskalar” firmy Apple nie jest właśnie nowa linia marketingowa; jest to architektura procesora, nad którą Apple pracuje od 2004 roku. W rzeczywistości Apple jest właścicielem co najmniej czterech przyznanych patentów na tę technologię, która jeszcze nie wyszła na jaw.

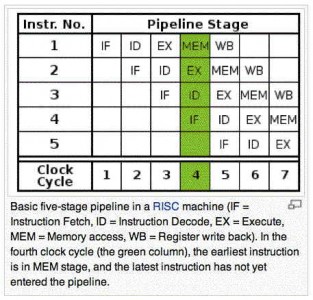

Apple pracuje nad tą technologią od 2004 roku i zasadniczo znacząco poprawia ona moc obliczeniową procesora poprzez odwrócenie uwagi od częstotliwości i włączenie jej potok instrukcji co umożliwiłoby procesorom wykonywanie większej liczby poleceń jednocześnie przy mniejszej liczbie przeszkód do pokonania. Szybkość to nie jedyna cecha nowych procesorów, gdyż do działania będą zużywać jeszcze mniej energii, dlatego mówimy o prawdziwym „asie w rękawie” dla Apple’a, który nie musiałby stosować czterordzeniowych procesorów w iDevices aby uzyskać zwiększoną wydajność.

Ponieważ częstotliwości zegara stale rosną w odpowiedzi na zwiększone wymagania dotyczące wydajności, wzrosła również moc, podczas gdy głębsze rurociągi wykazują malejący wpływ na liczbę instrukcji na cykl (IPC) osiągniętą w rzeczywistych sytuacjach, co dodatkowo przyczynia się do wzrostu mocy problem z rozpraszaniem spowodowany nieefektywnością. Na przestrzeni lat pojawiło się wiele mechanizmów próbujących uratować równoległość na poziomie instrukcji (ILP), takich jak SMT (jednoczesna wielowątkowość) i VLIW (bardzo długie słowo instrukcji) oraz wykonywanie poza kolejnością, niektóre z większym sukcesem niż inni. Klasyczną optymalizacją czasu kompilacji, która pozwala na bardziej efektywne wykorzystanie dłuższych potoków, jest rozwijanie pętli. Niestety, większości procesorów brakuje wymaganej liczby rejestrów programu, aby umożliwić wystarczające rozwijanie w celu pełnego nasycenia głębszych potoków. Zwiększanie liczby rejestrów bez utraty kompatybilności oprogramowania jest również problematyczne. Co więcej, wielu typów pętli po prostu nie da się rozwinąć, na przykład tych, które implementują przepływ sterowania zależny od danych, czyli tej samej klasy pętli, na które najbardziej narażone są głębsze potoki.

Choć sama technologia wygląda świetnie, problem polega na tym, że Apple może nie mieć jej gotowej do włączenia w chipie A6, który miałby być montowany w iPadzie 3 i iPhonie 5.

Ponieważ Apple dostarcza własne kompilatory, a także projektuje procesory, ma wyjątkową pozycję, aby zaoferować szerokiemu gronu programistów iOS kompletne rozwiązanie makroskalarne, jeszcze bardziej zwiększając różnicę ceny do wydajności między nim a potencjalnymi nabywcami iPada. Czy to przełom? Byłoby tak, gdyby obiecywana wydajność mogła zostać zrealizowana w praktyce. Będziemy musieli zobaczyć, jak dobrzy są inżynierowie kompilatorów Apple.