Förra veckan på Apple det var registrerat på honom ett patent på en teknik som kallas Makroskalär som har rollen att avsevärt förbättra prestandan hos en processor för mobila terminaler. Detta är företagets fjärde patent relaterat till denna teknik och det verkar som att Apple förbereder det för implementering i några av sina produkter. Den intressanta delen av denna teknik ligger i det faktum att Apple har patenterat den i flera länder runt om i världen, så det kan inom en snar framtid lansera en produkt som skulle kunna få den implementerad.

I början av förra veckan publicerade US Patent & Trademark Office en överraskande varumärkesansökan från Apple för ordet "Macroscalar". En andra varumärkesanmälan för detta dök också upp i Hongkongs IP Offices databas under helgen. Naturligtvis betyder en varumärkesanmälan i sig absolut ingenting. Men så är inte fallet här. Apples "Macroscalar" är det inte bara en ny marknadsföringslinje; det är en processorarkitektur som har varit på gång hos Apple sedan 2004. Faktum är att Apple äger minst fyra beviljade patent på tekniken som ännu inte har kommit fram.

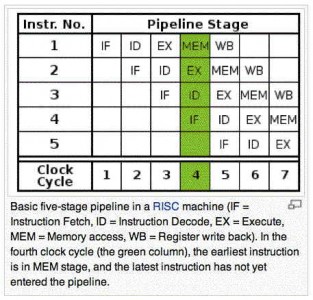

Apple har arbetat med den här tekniken sedan 2004 och i huvudsak förbättrar den beräkningskraften hos en processor avsevärt genom att ta bort fokus från frekvensen och sätta på den instruktion pipelining vilket skulle tillåta processorer att utföra fler kommandon samtidigt med färre hinder att övervinna. Hastighet är inte det enda kännetecknet för de nya processorerna eftersom de kommer att förbruka ännu mindre energi för att fungera, så vi pratar om ett riktigt "ess i rockärmen" för Apple, som inte skulle behöva använda fyrkärniga processorer i iDevices för att få höjda prestanda.

När klockfrekvenserna fortsätter att stiga som svar på ökade krav på prestanda har effekten också ökat, medan djupare pipelines har uppvisat en minskande effekt på antalet instruktioner per cykel (IPC) som uppnås i verkliga situationer, vilket ytterligare bidrar till kraften spridningsproblem genom ineffektivitet. En mängd olika mekanismer har dykt upp under åren som försöker rädda parallellism på instruktionsnivå (ILP), såsom SMT (samtidig multitrådning) och VLIW (mycket långt instruktionsord) och exekvering i oordning, några med större framgång än andra. Den klassiska optimeringen av kompileringstid som möjliggör ett mer effektivt utnyttjande av längre pipelines är loop-utrullning. Tyvärr saknar de flesta processorer det erforderliga antalet programregister för att tillåta tillräckligt med utrullning för att helt mätta djupare pipelines. Att öka antalet register utan att kompromissa med mjukvarukompatibiliteten är också problematiskt. Dessutom kan många typer av loopar helt enkelt inte rullas upp, till exempel de som implementerar databeroende kontrollflöde, vilket är samma klass av loopar som drabbas hårdast av djupare pipelines.

Även om själva tekniken ser bra ut, är problemet att Apple kanske inte har den redo för inkludering i A6-chippet som skulle ingå i iPad 3 och iPhone 5.

Eftersom Apple tillhandahåller sina egna kompilatorer såväl som designar processorer, är det unikt positionerat för att erbjuda en komplett makroskalär lösning till sitt stora band av iOS-utvecklare, vilket ytterligare breddar pris/prestandagapet mellan det och iPad-wannabes. Är det ett genombrott? Det kan vara om de effektivitetsvinster som utlovas kan realiseras i praktiken. Vi måste se hur bra Apples kompilatortekniker är.