Saptamana trecuta companiei Apple i-a fost inregistrat un brevet de inventie pentru o tehnologie numita Macroscalar care are rolul de a imbunatati semnificativ performantele unui procesor pentru terminale mobile. Acesta este al patrulea brevet de inventie al companiei care are legatura cu aceasta tehnologie si se pare ca Apple o pregateste pentru implementarea in unele produse ale sale. Partea interesanta a acestei tehnologii sta in faptul ca Apple a brevetat-o in mai multe tari de pe glob deci ar putea lansa in viitorul apropiat un produs care ar putea-o avea implementata.

Early last week the US Patent & Trademark Office published a surprising trademark application from Apple for the word “Macroscalar.” A second trademark filing for this also showed up in Hong Kong’s IP Office’s database over the weekend. Of course a trademark filing by itself means absolutely nothing. But that’s not the case here. Apple’s “Macroscalar” isn’t just a new marketing line; it’s a processor architecture that’s been in the works at Apple since 2004. In fact, Apple owns at least four granted patents on the technology that has yet to come to light.

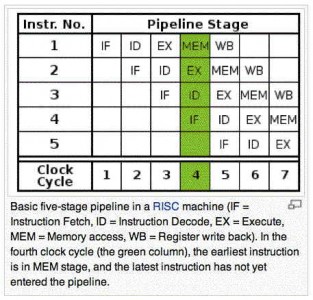

Apple lucreaza inca din anul 2004 la tehnologia aceasta si in esenta ea imbunatateste semnificativ puterea de calcul al unui procesor luand accentul de pe frecventa si punandu-l pe instruction pipelining care ar permite procesoarelor sa execute mai multe comenzi in acelasi timp avand de depasit mai putine obstacole. Rapiditatea nu este singura caracteristica a noilor procesoare deoarece acestea vor consuma si mai putina energie pentru a functiona deci vorbim despre un adevarat “as in maneca” pentru Apple care nu ar fi nevoita sa utilizeze procesoare quad-core in iDevice-uri pentru a obtine performante ridicate.

As clock frequencies continue to rise in response to increased demands for performance, power has also increased, while deeper pipelines have exhibited a diminishing effect on the number of instructions per cycle (IPC) achieved in real-world situations, which further contributes to the power dissipation problem through inefficiency. A variety of mechanisms have emerged over the years that attempt to salvage instruction-level parallelism (ILP), such as SMT (simultaneous multi-threading) and VLIW (very long instruction word) and out-of-order execution, some with more success than others. The classic compile-time optimization that permits more effective utilization of longer pipelines is loop unrolling. Unfortunately, most processors lack the requisite number of program registers to permit enough unrolling to fully saturate deeper pipelines. Increasing the number of registers without compromising software compatibility is problematic as well. Furthermore, many types of loops simply cannot be unrolled, such as those that implement data-dependent control-flow, which is the same class of loop hit hardest by deeper pipelines.

Desi tehnologia in sine pare grozava, problema este ca Apple s-ar putea sa nu o aiba pregatita pentru includerea in chip-ul A6 care ar urma sa fie inclus in iPad 3 si iPhone 5.

Since Apple provides its own compilers as well as designing CPUs, it is uniquely positioned to offer a complete macroscalar solution to its large band of iOS developers, further widening the price/performance gap between it and the iPad wannabes. Is it a breakthrough? It could be if the efficiencies it promises can be realized in practice. We’ll have to see just how good Apple’s compiler engineers are.